Heterogeneous Multicores SoC

Heterogeneous multicores afford consolidation of various systems that previously required individual devices or different systems running on separate devices.

The multi-core processor SoCs reduces BOM costs, power consumption and accelerate design implementation.

This kind of SoC provides the capacity to design -safety-criticality system on dedicated core and non-safe sytem running on other cores.

Applications are designed on symmetric multiprocessing (SMP) and asymmetric multiprocessing (AMP) systems.

- An SMP system is implemented on a homogeneous multicore platform where all the cores are identical. Linux runs across all the cores.

With SMP, tasks are distributed across the cores automatically by Linux or explicitly by the user programmatically on a specific core.

- AMP and Embedded Systems

AMP is implemented on a heterogeneous multicore platform where all the cores are not identical like imx8MP SoC: 4x cortex A53 cores (SMP) and 1x MCU cortex-M7 core.

In an AMP system, there is no unified operating system or scheduler managing all resources in the system. Debugging the disparate workloads running on the potentially heterogeneous cores can be quite challenging.

In AMP systems, following points needs to be considered and resolved:

- Boot order: the sequence in which the software on each core starts – may be important to avoid synchronization and security issues

- An inter-core communication facility issues that require the cores to be protected from one another.

- Debugging the different tasks running on the heterogeneous cores can be quite challenging.

We build AMP solutions based on following points

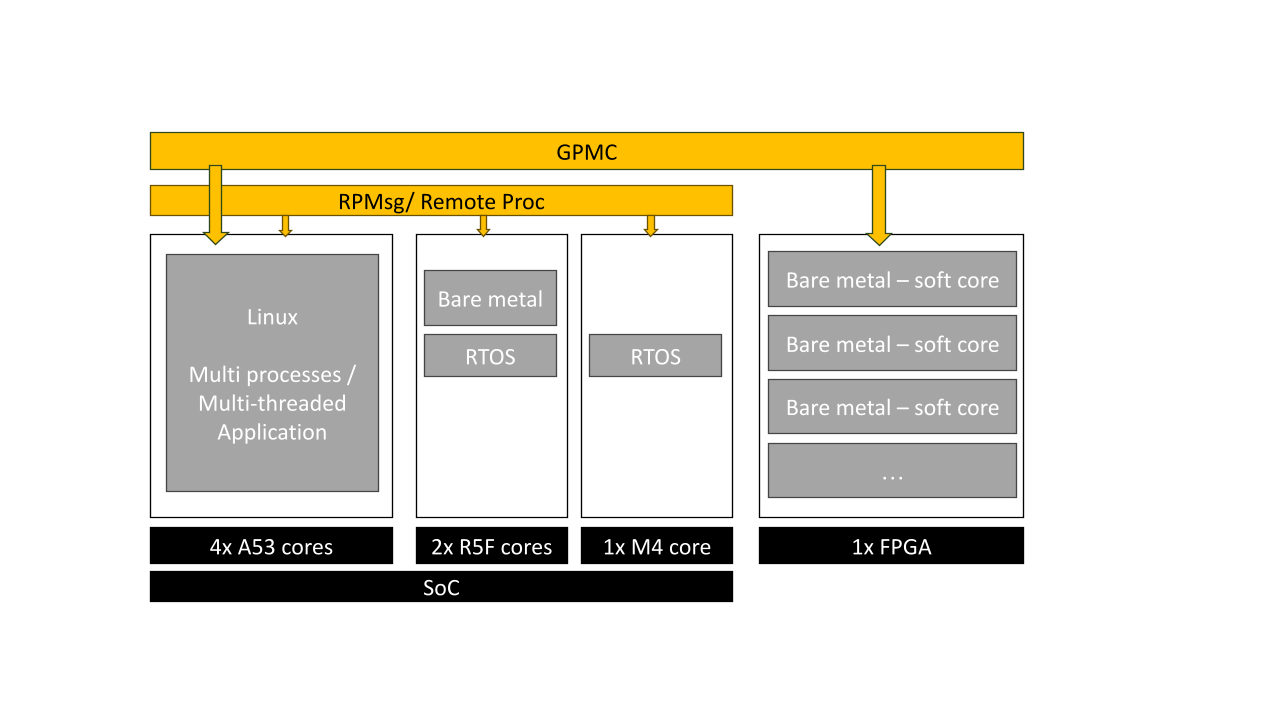

- Remoteproc: This component allows for the Life Cycle Management (LCM) of remote processors from software running on a master processor. It has the ability to load firmware and to start and stop remote processors.

- RPMsg: The RPMsg API facilitates Inter Processor Communications (IPC) between the independent software contexts running on heterogenous cores. It enables applications to send and receive variable length binary message data, with the message format being defined by the application. It is well suited for exchanging asynchronous and event-based messages with remote processors.

- Safety Critical features: The main requirement for a safety-critical system is the isolation to separate different software components from each other to isolate safe and non-safe features. The separation is required for the processing blocks, memory blocks, peripherals, and system function. If there is a system failure, the watchdog attached to the system can simply reboot the running embedded system without impacting the embedded systems running on other cores.

Bellow is represented the TI AM6442 SoC combined with a FPGA as proposed by the Phytec SOM AM64xx.